Avispado

Efficient RISC-V Core

A highly efficient and power-conscious core, ideal for AI edge and embedded applications.

Efficient RISC-V Core

A highly efficient and power-conscious core,

ideal for AI edge and embedded applications

64-bit In-Order Execution

Optimized for energy efficiency.

Vector-Ready

Supports RISC-V Vector Specification 1.0 for AI acceleration.

Ideal for

Machine Learning, Edge AI, IoT, and embedded computing.

Multiprocessing Support

Scalable to multi-core implementations, Linux Ready.

High Bandwidth Access

Gazzillion Technology™ ensures efficient data movement with up to 64 simultaneous memory requests.

Characteristics

(RISCV64GCV)

(AXI/CHI)

Available extensions

Customisable options

more info

Multiprocessor Ready

Avispado supports cache-coherent Multiprocessing environments. Its native CHI interface can be tailored down to AXI, depending on your needs.

Be it 2, 4, or hundreds of cores, Avispado is ready for your next SOC.

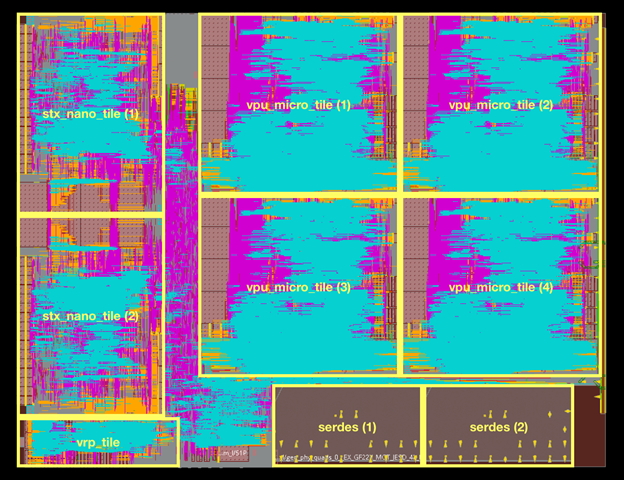

Avispado Test Chip